World’s First SiPho 1.6T-DR8 Transceiver with stacked TIA

Published: Wednesday March 11th, 2026 • In News • By Hanjo Rhee

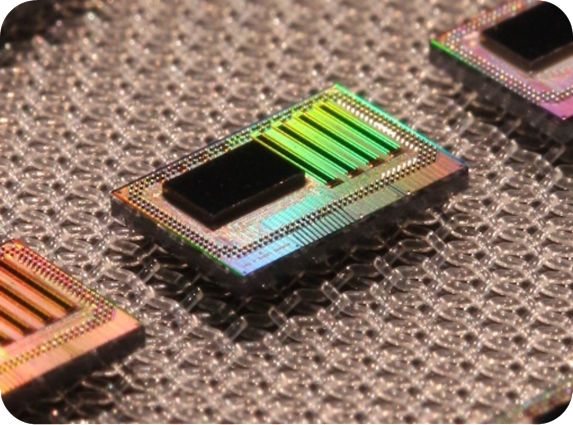

Los Angeles, USA – OFC 2026 – Sicoya GmbH (Germany), a leading supplier of high-performance silicon photonics chipsets for next-generation optical interconnects in AI and data center networks, and STMicroelectronics (NYSE: STM), a global semiconductor leader serving customers across the spectrum of electronics applications, today announced the successful development and customer sampling of a 1.6T-DR8 silicon photonics transceiver engine built on ST’s PIC100 silicon photonics platform and B55X BiCMOS technology, featuring vertically stacked TIA integration enabled through Chip-on-Wafer (CoW) technology.

The solution combines ST’s advanced process technologies with Sicoya’s TRX-1.6T-DR8 transceiver architecture, integrating transmitter and receiver functionality on a single die with stacked TIA implementation. This achievement represents a significant milestone in photonic-electronic cointegration and underscores Europe’s capability to deliver high-performance optical interconnect solutions at scale for next-generation AI and hyperscale data center infrastructure.

“The introduction of our 1.6T-DR8 chipset on STMicroelectronics’ PIC100 platform with stacked TIA is a defining milestone for European silicon photonics. With customer sampling underway, Sicoya is delivering scalable, high-density optical interconnect chipsets engineered to support the bandwidth, signal integrity demanded by AI- infrastructure at scale.” said Hanjo Rhee, CTO of Sicoya

Sicoya will showcase the TRX-1.6T-DR8 chipset at Booth 507, featuring a demonstration of the integrated TX/RX architecture with the stacked TIA in 200 Gb/s per lane operation. Samples are available to selected customers.

Sicoya Integrates Transmitter and Receiver on a Single Chip with Die-Stacked TIA for a Unique Transceiver Engine

At the core of the TRX-1.6T-DR8 platform is a singlechip approach that integrates both the transmitter and the receiver functions, including a die-stacked TIA within a single transceiver chipset. This integrated architecture is designed to address key deployment challenges in the transition for Silicon Photonics towards 400G per lane.

This highly integrated architecture enables Sicoya’s customers to:

- Realize best-in-class signal integrity performance, supported by a flip-chip-based vertical integration approach and a co-developed B55X TIA specifically aligned with the PIC100 photonic architecture, minimizing interconnect length, reducing parasitics, and providing tightly controlled high-speed electrical paths for 200G PAM4 operation and beyond

- Leverage a unified transceiver chipset integrating both transmitter and receiver functions, enabling a high integration level that supports compact 1.6T-class module implementations while reducing overall system complexity

- Adopt a forward-compatible platform architecture, designed to accommodate the industry’s transition toward 400G-per-lane technologies while preserving architectural continuity and investment stability

- Rely on scalable high-volume manufacturing, enabled by STMicroelectronics’ 300 mm PIC100 platform, which provides advanced semiconductor process control and substantial production capacity suited for hyperscaler deployment

For module manufacturers and hyperscale operators targeting (half-)retimed or unretimed 1.6T-DR8 modules, this integrated TX/RX platform establishes a scalable and future-ready foundation combining high-speed signal integrity, advanced integration density, and 300 mm manufacturing scalability within a resilient European semiconductor ecosystem.

STMicroelectronics’ PIC100 and B55X technologies enable next-generation optical interconnects for AI infrastructures

Built on ST’s 300 mm manufacturing line in Crolles (Europe, France), the PIC100 silicon photonics platform delivers state of the art performance for 200 Gb/s per lane optical interconnects. The technology combines ultra-low loss silicon and silicon nitride waveguides with high bandwidth modulators and photodiodes, as well as an innovative low loss edge coupling scheme optimized for automated fiber attach. This combination enables efficient, compact 800G and 1.6T engines while preserving the link budgets and energy per bit targets required by AI class datacenters.

Complementing PIC100, ST’s B55X BiCMOS platform provides the high-speed electronic companion functions needed for advanced optical engines, including TIAs and drivers operating at 200 Gb/s per lane and beyond. With fT/fmax of 400/500 GHz and excellent noise and linearity figures, B55X is ideally suited for stacked die integration with PIC100. This tightly co-optimized SiPho plus BiCMOS framework allows the Sicoya TRX-1.6T-DR8 engine to minimize parasitics, shorten high speed interconnect paths, and achieve best in class signal integrity in a very compact footprint.

“Sicoya’s innovative 1.6TDR8 engine clearly demonstrates how ST’s PIC100 silicon photonics, B55X BiCMOS, and advanced ChiponWafer packaging come together at scale to enable nextgeneration optical interconnects,” said Sylvie Gellida, General Manager, Optical and RF Foundry Division, STMicroelectronics. “This complete optical engine on our 300 mm manufacturing platform is a key differentiator for AI and hyperscale data center markets.”

PIC100 and B55X are both manufactured on ST’s industrial 300 mm infrastructure, giving customers access to CMOS class process control, high yield, and scalable capacity tailored to hyperscaler deployments. This same platform underpins ST’s long term roadmap toward TSV enabled photonic electronic integration for Near Packaged and Co Packaged Optics, ensuring that designs developed on the TRX-1.6T-DR8 engine can evolve smoothly toward future 400 Gb/s per lane and optical I/O architectures within a resilient European supply chain.

Read more about ST silicon photonics:

https://www.st.com/content/st_com/en/about/innovation—technology/silicon-photonics.html

About Sicoya

Sicoya GmbH develops and supplies highly integrated silicon photonics chipsets for next-generation optical interconnects used in AI and hyperscale data center infrastructure. The company’s technology integrates transmitter and receiver functionality on a single photonic integrated circuit (PIC) and combines it with advanced chip-on-wafer (CoW) stacked electronics, enabling compact optical engines with a high level of integration for high-speed transceivers.

This architecture supports lane rates of 200G and 400G per lane, low power consumption, and scalable manufacturing for next-generation data center networks. Sicoya works closely with leading semiconductor foundries and transceiver manufacturers across the global optical communications ecosystem.

Read more about Sicoya:

MEDIA CONTACT

Moritz Grehn, PhD

Head of Product Marketing

marketing@sicoya.com